# PowerPC User-Level Instruction Set **Quick Reference Card**

© Copyright 2010, Tennessee Carmel-Veilleux <<u>tcv@ro.boto.ca</u>>

Based on a mnemonic presentation idea from Bill Karsh in his PowerPC tutorial series in MacTech magazine (http://macte.ch/luHry)

### Notation

|        | Concatenation of bit blocks                                                                                        |

|--------|--------------------------------------------------------------------------------------------------------------------|

|        | Alternation                                                                                                        |

| UIMMnn | Unsigned immediate of $nn$ bits (ie: UIMM16 = 16 bits)                                                             |

| SIMMnn | Signed immediate of nn bits (ie: $SIMM26 = 26$ bits)                                                               |

| EXT    | Sign-extend to word                                                                                                |

| (rA 0) | In some instances, value "0" for register rA (meaning r0) is a special case that actually means "use the value 0". |

|        |                                                                                                                    |

- <> List of functional suffixes (append 0 or 1 from the list)

- [] List of optional suffixes (0 or more, in the order specified)

Example of multiple suffixes for an instruction:

add < c | e | me | ze < [ o, . ]; add. addc. addme. addze. addo. addco.addeo, addmeo, addzeo, add., addc., adde., addme., addze., addo., addeo., addmeo., addzeo. are all valid.

# **Registers**

- r0-r31: General-purpose integer registers

- LR: Link register, saves return address of branches that link

- CTR: Counter for auto-decrementing loops

- CR: Condition register

- composed of 8 condition records (CR0-CR7)

- saves results of comparisons and ALU operations CR0 CR7 CR1 Λ 28 31

# Label suffixes

Assemblers general recognize several suffixes for labels and values. These suffixes provide ways to extract only parts of an operand for use in immediate values.

- VALUE@h: Only the high 16-bit part (bits 0-15).

- VALUE@ha: Like @h, but adjusted to compensate for sign extension applied by an "addi VALUE@l" on the same register.

- VALUE@I: Only the low 16-bit part (bits 16-31).

NOTE: Compare the following two ways to load an immediate value into a register (equivalent in result but different in spirit):

| 1. | addis<br>addi | rD, 0, VALUE@ha<br>rD, rD, VALUE@l |

|----|---------------|------------------------------------|

| 2. | addis<br>ori  | rD, 0, VALUE@h<br>rD, rD, VALUE@l  |

With the first method, the addi instruction does sign extension on its 16-bit signed immediate operand. If we want to load, for instance 0x12348765, the value 0x8765 from "0x12348765@l" will be signextended to 0xFFFF8765. This will cause an off-by-one error if we add it with 0x12340000 from addis rD,0, 0x12348765@h. The @ha suffix verifies this condition ("negative" low 16 bits) and adjusts the high-part so that when it is added with the sign-extended low part, the result correct: 0x12348765 in our case. With the second method, using ori which does not sign-extend its operand, the high part requires no adjustment.

# Load and store instructions

#### Addressing modes

The PowerPC has only two addressing modes, but combining them with the load/store instructions options yields many possibilities. The addressing modes (using lwz as an example) are:

• lwz rD, offset(rA|0)  $\rightarrow$  Register-indirect with immediate offset  $\rightarrow$  EA = (rA + offset) or (0 + offset)

$\rightarrow$  Offset is a 16 bit signed immediate value

• lwzx rD, (rA|0), rB  $\rightarrow$  Register-indirect with indexing  $\rightarrow EA = (rA + rB) \text{ or } (0 + rB)$

### Single loads and stores

| Instruction                  | Operation                                            |

|------------------------------|------------------------------------------------------|

| lbz[u,x] rD,d(rA)            | $rD \leftarrow byte from MEM[EA]$                    |

| lhz[u,x] rD,d(rA)            | $rD \leftarrow half$ -word from MEM[EA]              |

| lha[u,x] rD,d(rA)            | $rD \leftarrow sign-extended half word from MEM[EA]$ |

| lwz[u,x] rD,d(rA)            | $rD \leftarrow word from MEM[EA]$                    |

| <pre>stb[u,x] rS,d(rA)</pre> | $rS[24:31] \rightarrow MEM[EA]$ (store byte)         |

| <pre>sth[u,x] rS,d(rA)</pre> | $rS[16:31] \rightarrow MEM[EA]$ (store half-word)    |

| stw[u,x] rS,d(rA)            | $rS \rightarrow MEM[EA]$ (store word)                |

- "z" load suffix: treat as unsigned, zero-extend, right-justify.

- "a" load suffix: "algebraic": sign-extend to word.

- [u]: "update": if (rA != 0) then rA  $\leftarrow$  EA after load or store. In the case of loads, condition (rD = rA) also applies (logically so).

- [x]: "with indexing" (see addressing modes above), use operands as in "lwzx rD, (rA|0), rB" instead of "lwz rD, d(RA)".

#### **Multiple loads and stores**

| Instruction                                                  | Operation                                                                                                                                                                                                       |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lmw rD,d(rA)                                                 | n = (32 - rD); n consecutive words startingat EA are loaded into GPRs rD through r31.For example : Imw r29,0(r8) loads r29, r30and r31 from consecutive, increasingaddresses starting at EA.                    |

| stmw rS,d(rA)                                                | n = (32 - rS); n consecutive words starting<br>at EA are stored from the GPRs rS through<br>r31. For example, if rS = 29, r29, 30 and<br>r31 are stored at consecutive, increasing<br>addresses starting at EA. |

| String loads and stores (lsw because they are not available) | i, lswx, stswi, stswx) are omitted for brevity and<br>ble on all PPCs.                                                                                                                                          |

Arithmetic and logic instructions

#### Addition, subtraction, negation

| Instruction                     | Operands       | Operation                                                  |

|---------------------------------|----------------|------------------------------------------------------------|

| add <c,e>[o,.]</c,e>            | rD,rA,rB       | $rD \leftarrow rA + rB$                                    |

| addi <s,c,c.></s,c,c.>          | rD,(rA 0),SIMM | $rD \leftarrow (rA 0) + EXT(SIMM16)$                       |

| addme[o,.]                      | rD,rA          | $rD \leftarrow rA + XER[CA] - 1$                           |

| addze[o,.]                      | rD,rA          | $rD \leftarrow rA + 0 + XER[CA]$                           |

| neg[o,.]                        | rD,rA          | $rD \leftarrow (\neg rA + 1)$<br>(2's complement negation) |

| <pre>subf<c,e>[o,.]</c,e></pre> | rD,rA,rB       | $rD \leftarrow rB - rA$                                    |

| subfic                          | rD,rA,SIMM     | $rD \leftarrow EXT(SIMM16) - rA$                           |

| <pre>subfme[o,.]</pre>          | rD,rA          | $rD \leftarrow -1 - rA + XER[CA]$                          |

| <pre>subfze[o,.]</pre>          | rD,rA          | $rD \leftarrow 0 - rA + XER[CA]$                           |

• "i" suffix: "immediate": second operand is 16-bit sign-extended immediate value.

- "s" suffix: "shifted": immediate value is logical shifted left 16 bits prior to being used.

- "z" suffix: replaces rB with immediate value 0 (0x0000000).

- "m" suffix: replaces rB with immediate value -1 (0xFFFFFFF).

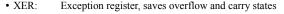

- "e" suffix: extended add or subtract. The value of XER[CA] is added to the result, enabling multi-word carry arithmetic. The value of XER[CA] is updated by these operations also.

- "c" suffix: carry updated. XER[CA] is updated with the operation's carry state (by default, the carry is unaffected).

- [0]: overflow updated. XER[OV] and XER[SO] are updated according to whether the operation overflows or not.

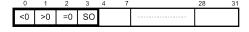

- [.]: Record result of operation in CR0 (<0, >0, =0, SO)

#### **Bitwise logical operations and shifts**

| Instruction          | Operands   | Operation                                                           |

|----------------------|------------|---------------------------------------------------------------------|

| and[c,.]             | rD,rA,rB   | $rD \leftarrow rA \wedge rB$                                        |

| andi.                | rD,rA,UIMM | $rD \leftarrow rA \land UIMM16$                                     |

| andis.               | rD,rA,UIMM | $rD \leftarrow rA \land (UIMM16 << 16)$                             |

| <pre>cntlzw[.]</pre> | rD,rA      | $rD \leftarrow number of leading zeros in rA$                       |

| eqv[.]               | rD,rA,rB   | $rD \leftarrow \neg(rA \oplus rB) \text{ (would be "xnor")}$        |

| <pre>extsb[.]</pre>  | rD,rA      | $rD \leftarrow EXT(rA[24:31])$ (sign-extend<br>low byte of rA)      |

| <pre>extsh[.]</pre>  | rD,rA      | $rD \leftarrow EXT(rA[16:31])$ (sign-extend<br>low half-word of rA) |

| nand[.]              | rD,rA,rB   | $rD \leftarrow \neg (rA \wedge rB)$                                 |

| nor[.]               | rD,rA,rB   | $rD \leftarrow \neg(rA \lor rB)$                                    |

| or[c,.]              | rD,rA,rB   | $rD \leftarrow rA \lor rB$                                          |

| ori                  | rD,rA,UIMM | $rD \leftarrow rA \lor (UIMM16)$                                    |

| oris                 | rD,rA,UIMM | $rD \leftarrow rA \lor (UIMM16 << 16)$                              |

| slw[.]               | rD,rA,rB   | $rD \leftarrow rA \leq rB[26:31]$ (logical)                         |

| srw[.]               | rD,rA,rB   | $rD \leftarrow rA \gg rB[26:31]$ (logical)                          |

| srawi[.]             | rD,rA,UIMM | $rD \leftarrow rA >> UIMM5$ (arithmetic)                            |

| sraw[.]              | rD,rA,rB   | $rD \leftarrow rA >> rB[26:31]$ (arithmetic)                        |

| <pre>xor[c,.]</pre>  | rD,rA,rB   | $rD \gets rA \oplus rB$                                             |

| xori                 | rD,rA,UIMM | $rD \leftarrow rA \oplus (UIMM16)$                                  |

| xoris                | rD,rA,UIMM | $rD \leftarrow rA \oplus (UIMM16 << 16)$                            |

• [c]: Complement (invert) the value from rB prior to using it. The actual value residing in rB is unaffected.

• [.]: Record result of operation in CR0 (<0, >0, =0, SO)

• NOTE: on shifts, values 0-32 are valid. For arithmetic shift rights, a value of 32 fills the word with the sign bit. For logical shift lefts, a value of 32 sets the word to 0.

#### **Multiplication**

| Inst. | Operands   | Operation                                                               |

|-------|------------|-------------------------------------------------------------------------|

| mulhw | rD,rA,rB   | $rD \leftarrow rA \times rB$ (32 upper bits of 64-bit result)           |

| mulli | rD,rA,SIMM | $rD \leftarrow (rA \times SIMM16)$ (32 lower bits of 48-<br>bit result) |

| mullw | rD,rA,rB   | $rD \leftarrow rA \times rB$ (32 lower bits of 64-bit result)           |

## Division

| Inst.             | Operands | Operation                  |

|-------------------|----------|----------------------------|

| divw <u>[o,.]</u> | rD,rA,rB | $rD \leftarrow rA \div rB$ |

|                   | . 1      |                            |

• "u" suffix: treat operands as unsigned numbers

• [o]: Record overflow of result

• [.]: Record result of operation in CR0 (<0, >0, =0, SO)

### Rotate and mask

| Inst.     | Operands         | Operation                                                                 |

|-----------|------------------|---------------------------------------------------------------------------|

| rlwimi[.] | rD,rA,UIMM,MB,ME | $rD \leftarrow rotate rA left by UIMM bits, mask and insert result in rD$ |

| rlwinm[.] | rD,rA,UIMM,MB,ME | $rD \leftarrow rotate rA left by UIMM bits and mask$                      |

| rlwnm[.]  | rD,rA,rB,MB,ME   | $rD \leftarrow rotate \ rA \ left \ by \ rB \ bits \ and mask$            |

· For all these instructions, a mask M is built by starting with a zeroword (0x0000000) and setting bits to "1" starting at bit number MB and ending at bit number ME, both inclusive. It is possible to wrap-around while generating the mask (ie: MB > ME).

### Examples:

MASK(MB.ME) with MB=29 and ME=3:

| 10 | 1 | 2 ( | 3 ME | 4 | 5 | 9 | 7 | ~ | 6 | 10 | Π | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 MB | 30 [ | 31 ( |

|----|---|-----|------|---|---|---|---|---|---|----|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------|------|------|

| 1  | 1 | 1   | 1    | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1     | 1    | 1    |

### MASK(MB,ME) with MB=8 and ME=14:

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 MB | 16 | 101 | 11 | 12 ( | 13 ( | 14 ME | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

|---|---|---|---|---|---|---|---|------|----|-----|----|------|------|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1    | 1  | 1   | 1  | 1    | 1    | 1     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

### rlwimi r3,r4,6,20,25 (r4 = 0x0FF0\_0017, r3 = 0x12AB\_CDEF)

- 1. Generate mask : MASK(20,25) = 0x0000 0FC0 = 0xFC00 05C3 2. Rotate source: tmp1 = r4 ROL 6

- 3. Extract field:  $tmp2 = tmp1 \land MASK = 0x0000_05C0$

- 4 Mask destination:  $tmp3 = r3 \land \neg MASK = 0x12AB C02F$

- 5. Insert field in destination:  $r3 \leftarrow tmp2 \lor tmp3$ = 0x12AB C5EF

The previous 5 steps as binary:

- 1. 0b0000 0000 0000 0000 0000 1111 1100 0000

- 2. 0b1111 1100 0000 0000 0000 0101 1100 0011

- 3. 0b0000\_0000\_0000\_0000\_0000\_0101\_1100\_0000

- 4. 0b0001 0010 1010 1011 1100 **0000 00**10 1111

- 5. 0b0001\_0010\_1010\_1011\_1100\_0101\_1110\_1111

rlwinm  $r_{3}, r_{4}, 12, 20, 31$  (r4 = 0x5A70 00BB)

| 1. | Generate mask :               | MASK(20,31)                    | = 0x0000_0FFF |

|----|-------------------------------|--------------------------------|---------------|

| 2. | Rotate source:                | tmp1 = r4 ROL 12               | = 0x000B_B5A7 |

| 3. | Extract field in destination: | $r3 \leftarrow tmp1 \lor MASK$ | = 0x0000 05A7 |

# **Comparison instructions**

| Inst. | Operands      | Operation                                    |  |

|-------|---------------|----------------------------------------------|--|

| cmp   | crD,L,rA,rB   | Compare signed rA to rB                      |  |

| cmpi  | crD,L,rA,SIMM | Compare signed rA to EXT(SIMM16)             |  |

| cmpl  | crD,L,rA,rB   | Compare unsigned rA to rB                    |  |

| cmpli | crD,L,rA,UIMM | Compare unsigned rA to<br>(0x0000    UIMM16) |  |

crD can be omitted. In that case, the assembler assumes cr0.

- The L field means "Long" (64-bit compare) if set to "1", or 32-bit compare if set to "0". On 32-bit PowerPC, L should always be set to "0". Because of this, a simplified mnemonic exists for all "cmp"-series instructions: "cmpw crD, rA, rB" is equivalent to "cmp crD,0,rA,rB", etc.

- For all these instructions, the result of a comparison from rA to (rB|SIMM|UIMM) is stored in the specified condition register crD. For example, cmp 3,0,rA,rB would yield cr3 = "100 || XER[S0]" if rA < rB,  $cr3 = "010 \parallel XER[S0]$ " if rA > rB and  $cr3 = "001 \parallel$ XER[SO]" if rA = rB.

# Condition register manipulation instructions

| Inst.  | Operands       | Operation                                      |  |

|--------|----------------|------------------------------------------------|--|

| crand  | crbD,crbA,crbB | $crbD \leftarrow crbA \wedge crbB$             |  |

| crandc | crbD,crbA,crbB | $crbD \leftarrow crbA \land \neg crbB$         |  |

| creqv  | crbD,crbA,crbB | $crbD \leftarrow \neg (crbA \oplus crbB)$      |  |

| crnand | crbD,crbA,crbB | $crbD \leftarrow \neg (crbA \land crbB)$       |  |

| crnor  | crbD,crbA,crbB | $crbD \leftarrow \neg (crbA \lor crbB)$        |  |

| cror   | crbD,crbA,crbB | $crbD \leftarrow crbA \lor crbB$               |  |

| crorc  | crbD,crbA,crbB | $crbD \leftarrow crbA \lor \neg crbB$          |  |

| crxor  | crbD,crbA,crbB | $crbD \leftarrow crbA \oplus crbB$             |  |

| mcrf   | crD,crA        | $crD \leftarrow crA (move field A to field D)$ |  |

| crclr  | crbD           | Simplified for crxor crbD, crbD, crbD          |  |

| crmove | crbD,crbA      | Simplified for cror crbD, crbA, crbA           |  |

| crnot  | crbD,crbA      | Simplified for crnor crbD, crbA, crbA          |  |

| crset  | crbD           | Simplified for creqv crbD, crbD, crbD          |  |

• For the cr<OP> instructions, operands crb[A,B,D] mean "condition register bit", with value 0-31. All of these instructions carry-out logical operations between single bits of the CR, no matter what the conventional "meanings" of the bits are (<0, >0, =0, SO).

# Example:

• cror 0,5,6: CR[0]  $\leftarrow$  CR[5]  $\lor$  CR[6], thus cr0[=0]  $\leftarrow$  1, if cr1 had ">=" comparison result, otherwise  $cr0[=0] \leftarrow 0$ .

## **Branch instructions**

The PowerPC architecture uses a very flexible branching unit to decode the several fields contained in branch instructions. We will cover the basic branch instructions and their fields, and then present tables and examples of simplified branch mnemonics.

### Field names

- <u>BI (Branch Input)</u>: which bit of the CR is used as a branch condition

- BO (Branch Options): how to treat CTR and BI to determine if branching occurs

- Target: where to branch

### **Branch instructions**

| Inst.    | Operands     | Operation                   |

|----------|--------------|-----------------------------|

| b[1,a]   | target       | Branch unconditionally      |

| bc[1,a]  | BO,BI,target | Branch conditionally        |

| bclr[1]  | BO,BI        | Branch to LR conditionally  |

| bcctr[1] | BO,BI        | Branch to CTR conditionally |

- [1]: linking: store current PC + 4 in LR, so that a "blr" instruction can be used to return from a function call.

- [a]: absolute: target is an absolute address instead of a PC-relative displacement.

- For the b[1,a] instruction, target is a 26-bit signed immediate with 2 LSbs always "0" (4-bytes aligned). Maximum branch distance is [-33,554,432...33,554,428].

- For the bc[1,a] instruction, target is a 16-bit signed immediate with 2 LSbs always "0" (4-bytes aligned). Maximum branch distance is [-32,768...32764].

- In the case of non-absolute (no [a] option) branches, the target displacement is added to PC. A displacement of 0 is an infinite loop at the current PC. For the unconditional branch ([a] option), the target is still signed, but the displacement is based around 0x0000 0000.

- To obtain the value of PC, one can branch linking to the next instruction (b1 +4). The LR will contain the PC value at that next instruction. This trick is used by compilers to access local constant pools inserted after function return instructions.

- PowerPC assemblers and linkers will always adjust relocations so that displacements and labels can be specified directly, without having to adjust the value formats to the field formats. For example, "b +8" will get encoded as a target of 0x000002 (stripped of the 2 LSbs) automatically in the instruction.

- BI values can be simplified with constants named cr0 through cr7 with values 0-7 respectively and constants named lt,gt,eq,so with values 0-3 respectively. Then, cr4[<0], which is BI=16 can be written as (cr4\*4)+lt.

# **BO values**

| BO    | Branch if                                                    | Symbol |

|-------|--------------------------------------------------------------|--------|

| 0000y | Decremented CTR $\neq 0$ and the condition is <b>false</b> . | dnzf   |

| 0001y | Decremented $CTR = 0$ and the condition is <b>false</b> .    | dzf    |

| 001zy | Branch if the condition is <b>false</b> .                    | f      |

| 0100y | Decremented CTR $\neq 0$ and the condition is <b>true</b> .  | dnzt   |

| 0101y | Decremented $CTR = 0$ and the condition is <b>true</b> .     | dzt    |

| 011zy | Branch if the condition is <b>true</b> .                     | t      |

| 1z00y | Decremented CTR $\neq$ 0 (only CTR checked).                 | dnz    |

| 1z01y | Decremented $CTR = 0$ (only CTR checked).                    |        |

| 1z1zz | Branch always.                                               | -      |

- Symbols (3<sup>rd</sup> column of table above): the "c" of "bc" and the BO field value can be omitted and replaced with one of these symbols as a suffix. For example, and assuming y=z=0, the instruction "bc 8,5,1abe1" can be replaced with "bdnzt 5,1abe1".

- "y" bits are "branch likely to be taken" hints if set to "1". This is ignored by many implementations. A suffix of "-" added to the instruction clears this bit (branch not likely taken). A suffix of "+" added to the instruction sets this bit (branch likely taken). Example: "bdnzt+ 5,label" is equivalent to "bc 9,5,label". Many processors of the PowerPC family ignore this hint.

- "z" bits should be zeroed as they are for future extensions.

# Examples:

- bc 8,5,1abel : Branch if decremented  $CTR \neq 0$  and CR[5] = "1".

- bdnzt 5, label : same as above.

- bdnzt (cr1\*4)+gt,label : same as above.

- bl label: Branch and link to label (call function, return with blr).

- blr: Branch unconditional to LR (return from function).

- bdza label: Branch absolute to label if decremented CTR = 0.

- btctr lt: Branch to CTR if cr0[<0](CR[0]) = "1".

- bf eq,label: Branch to label if cr0[=0] (CR[2]) = "0".

# Simplified branches (or "classic" branches)

There are simplified "branch conditional" mnemonics that emulate the classic branches of other instruction sets. These mnemonics are for instructions that do not test the CTR.

| Instruction Operands            |              | Operation                   |

|---------------------------------|--------------|-----------------------------|

| <pre>b<test>[1,a]</test></pre>  | [crN,]target | Branch conditionally        |

| <pre>b<test>lr[1]</test></pre>  | [crN]        | Branch to LR conditionally  |

| <pre>b<test>ctr[1]</test></pre> | [crN]        | Branch to CTR conditionally |

• [crN] is an optional CR subfield number (ie: cr0-cr7), on which the test will take place. If omitted, the default is cr0.

## Simplified branches tests (using b<test> as example)

| Symbol             | Branch if                                                |  |

|--------------------|----------------------------------------------------------|--|

| b <u>eq</u>        | Equal, or zero (cr[=0] = "1")                            |  |

| b <u>ge</u>        | Greater than or equal $(cr[>0] = "1" \lor cr[=0] = "1")$ |  |

| b <u>gt</u>        | Greater than (cr[>0] = "1")                              |  |

| b <u>le</u>        | Less than or equal $(cr[<0] = "1" \lor cr[=0] = "1")$    |  |

| b <u>1t</u>        | Less than (cr[<0] = "1")                                 |  |

| b <u>ne</u>        | No equal, or not zero (cr[=0] = "0")                     |  |

| b <u>ng</u>        | Not greater than (equivalent to ble)                     |  |

| b <u><b>n1</b></u> | Not less than (equivalent to bge)                        |  |

| b <u>ns</u>        | Not summary overflow (cr[50] = "0")                      |  |

| b <u>so</u>        | Summary overflow (cr[S0] = "1")                          |  |

# Examples:

- bne label : Branch to label if cr0[=0] = "0".

- bsola cr2,label : Branch absolute linking to label if cr2[S0] = "1".

- b<u>lt</u>l label : Branch linking to label if cr0[<0] = "1".

- begctr cr4 : Branch to CTR if cr4[=0] = "1".

- bgtlrl : Branch linking to LR if cr0[>0] = "1".

- bl label: Branch and link to label (call function, return with blr).

- blr: Branch unconditional to LR (return from function).

# Special Purpose Register (SPR) Operations

| Inst. | Operands | Operation                                      |  |

|-------|----------|------------------------------------------------|--|

| mcrxr | crD      | $crD \leftarrow XER[0:3]$ then zero $XER[0:3]$ |  |

| mfcr  | rD       | $rD \leftarrow CR[0:31]$                       |  |

| mfspr | rD,SPR   | $rD \leftarrow SPR$                            |  |

| mtcrf | crM,rS   | CR updated with rS[crM] (see notes below)      |  |

| mtspr | SPR,rS   | SPR ← rS                                       |  |

| mtcr  | rS       | Simplified for mtcrf 0xFF, rS                  |  |

- crM is an 8 bit immediate mask (value 0x00-0xFF). The MSb means cr0, the LSb means cr7, and bits in between mean cr1-cr6. For example, crM = 0xA2 = 0b1010\_0010 would mean to load cr0, cr2 and cr6 from rS into the CR, and leave the other fields (cr1,cr3,cr4,cr5 and cr7) intact.

- There are simplified mtspr mnemonics for several SPRs which allow the omission of the SPR number: mt<u>ctr</u>, mt<u>lr</u>, mt<u>xer</u>.

- There are simplified mfspr mnemonics for several SPRs which allow the omission of the SPR number: mfctr, mflr, mfxer.

# **Trap and System Call Instructions**

| Inst. | Operands   | Operation                                |  |

|-------|------------|------------------------------------------|--|

| sc    | _          | System call                              |  |

| tw    | TO,rA,rB   | Trap if rA <to> rB is true</to>          |  |

| twi   | TO,rA,SIMM | Trap if rA <to> EXT(SIMM16) is true</to> |  |

• TO is a 5-bit field of conditions to test. If any of the conditions are met, the trap is taken.

- TO[0] (ie: mask = 0b10000) means (a < b)

- TO[1] (ie: mask = 0b01000) means (a > b)

- TO[2] (ie: mask = 0b00100) means (a = b)

- TO[3] means (a < b) with unsigned compare

- TO[4] means (a > b) with unsigned compare

# **Condensed alphabetical instructions list**

| Instruction |                | Operation                          |

|-------------|----------------|------------------------------------|

| add[.]      | rD,rA,rB       | Add                                |

| addc[o,.]   | rD,rA,rB       | Add, saving carry                  |

| adde[o,.]   | rD,rA,rB       | Add extended (adding carry)        |

| addi        | rD,(rA 0),SIMM | Add immediate                      |

| addis       | rD,(rA 0),SIMM | Add immediate shifted              |

| addic[.]    | rD,(rA 0),SIMM | Add immediate shifted saving carry |

| addme[o,.]  | rD,rA          | Add to minus one, extended         |

| addze[o,.]  | rD,rA          | Add to zero, extended              |

| and[.]      |                | AND                                |

| andc[.]     |                | AND with complement                |

| andi.       | rD,rA,UIMM     | AND with immediate                 |

| andis.      | rD,rA,UIMM     | AND with shifted immediate         |

| b[1,a]      | target         | Branch always                      |

| bc[l,a]     | BO,BI,target   | Branch conditionally               |

| bcctr[1]    | BO,BI          | Branch conditionally to CTR        |

| bclr[1]     | BO,BI          | Branch conditionally to LR         |

| beq[1,a]    | [crN,]target   | Branch on equal (or zero)          |

| bge[l,a]    | [crN,]target   | Branch on greater than or equal    |

| bgt[l,a]    | [crN,]target   | Branch on greater than             |

| ble[1,a]    | [crN,]target   | Branch on lower than or equal      |

| blt[l,a]    | [crN,]target   | Branch on lower than               |

| bne[1,a]    | [crN,]target   | Branch on not equal (or non-zero)  |

| bng[l,a]    | [crN,]target   | Branch on not greater than         |

| bnl[l,a]    | [crN,]target   | Branch on not lower than           |

|             |                |                                    |

| bnc[1 a]                     | [cnN ]tanget                     | Branch on not summary overflow                  |

|------------------------------|----------------------------------|-------------------------------------------------|

| <pre>bns[1,a] bso[1,a]</pre> | [crN,]target                     | Branch on not summary overflow                  |

|                              | [crN,]target                     | Branch on summary overflow                      |

| cmp<br>cmpi                  | [crD,]L,rA,rB<br>[crD,]L,rA,SIMM | Compare signed<br>Compare signed with immediate |

| -                            |                                  | 1 0                                             |

| cmpl                         | [crD,]L,rA,rB                    | Compare unsigned                                |

| cmpli                        | [crD,]L,rA,UIMM                  | Compare unsigned with immed.                    |

| cntlzw[.]                    | rD,rA                            | Count leading zeros in word                     |

| crand                        | crbD,crbA,crbB                   | AND on CR bits                                  |

| crandc                       | crbD,crbA,crbB                   | AND complemented on CR bits                     |

| crclr                        | crbD                             | Clear CR bit                                    |

| creqv                        | crbD,crbA,crbB                   | EQV on CR bits                                  |

| crmove                       | crbD,crbA                        | Move CR bit                                     |

| crnand                       | crbD,crbA,crbB                   | NAND on CR bits                                 |

| crnor                        | crbD,crbA,crbB                   | NOR on CR bits                                  |

| crnot                        | crbD,crbA                        | NOT on CR bit                                   |

| cror                         | crbD,crbA,crbB                   | OR on CR bits                                   |

| crorc                        | crbD,crbA,crbB                   | OR complemented on CR bits                      |

| crset                        | crbD                             | Set CR bit                                      |

| crxor                        | crbD,crbA,crbB                   | XOR on CR bits                                  |

| divw[o,.]                    | rD,rA,rB                         | Divide word                                     |

| divwu[o,.]                   | rD,rA,rB                         | Divide word unsigned                            |

| eqv[.]                       | rD,rA,rB                         | EQV (NOT (rA XOR rB)                            |

| extsb[.]                     | rD,rA                            | Sign-extend byte                                |

| extsh[.]                     | rD,rA                            | Sign-extend half-word                           |

| lbz[u,x]                     | rD,d(rA)                         | Load byte unsigned                              |

| lha[u,x]                     | rD,d(rA)                         | Load half-word and sign-extend                  |

| lhz[u,x]                     | rD,d(rA)                         | Load half-word unsigned                         |

| lmw                          | rD,d(rA)                         | Load multiple words                             |

| lwz[u,x]                     | rD,d(rA)                         | Load word                                       |

| mcrf                         | crD,crA                          | Move condition register field                   |

| mcrxr                        | crD                              | Move XER[0:3] to CR field                       |

| mfcr                         | rD                               | Move from CR                                    |

| mfspr                        | rD,SPR                           | Move from SPR                                   |

| mtcr                         | rS                               | Move to CR                                      |

| mtcrf                        | crM,rS                           | Update CR fields                                |

| mtspr                        | SPR,rS                           | Move to SPR                                     |

| mulhw                        | rD,rA,rB                         | Multiply high word                              |

| L                            |                                  |                                                 |

| mulli                  | rD,rA,SIMM       | Multiply low immediate                     |

|------------------------|------------------|--------------------------------------------|

| mullw                  | rD,rA,rB         | Multiply low word                          |

| nand[.]                | rD,rA,rB         | NAND                                       |

| neg[o,.]               | rD,rA            | Negate (2's complement)                    |

| nor[.]                 | rD,rA,rB         | NOR                                        |

| or[.]                  | rD,rA,rB         | OR                                         |

| orc[.]                 | rD,rA,rB         | OR with complement                         |

| ori                    | rD,rA,UIMM       | OR with immediate                          |

| oris                   | rD,rA,UIMM       | OR with shifted immediate                  |

| rlwimi[.]              | rD,rA,UIMM,MB,ME | Rotate left word immediate and mask insert |

| rlwinm[.]              | rD,rA,UIMM,MB,ME | Rotate left word immediate and mask        |

| rlwnm[.]               | rD,rA,rB,MB,ME   | Rotate left word and mask                  |

| sc                     |                  | System call                                |

| slw[.]                 | rD,rA,rB         | Shift left word (logical)                  |

| <pre>sraw[.]</pre>     | rD,rA,rB         | Shift right word (arithmetic)              |

| srawi[.]               | rD,rA,UIMM       | Shift right immediate (arithmetic)         |

| <pre>srw[.]</pre>      | rD,rA,rB         | Shift right word (logical)                 |

| stb[u,x]               | rS,d(rA)         | Store byte                                 |

| sth[u,x]               | rS,d(rA)         | Store half-word                            |

| stmw                   | rS,d(rA)         | Store multiple words                       |

| stw[u,x]               | rS,d(rA)         | Store word                                 |

| <pre>subf[o,.]</pre>   | rD,rA,rB         | Subtract from                              |

| <pre>subfc[o,.]</pre>  | rD,rA,rB         | Subtract from, update carry                |

| <pre>subfe[o,.]</pre>  | rD,rA,rB         | Subtract from, extended                    |

| subfic                 | rD,rA,SIMM       | Subtract from immediate, update carry      |

| <pre>subfme[o,.]</pre> | rD,rA            | Subtract from -1, extended                 |

| <pre>subfze[o,.]</pre> | rD,rA            | Subtract from 0, extended                  |

| tw                     | TO,rA,rB         | Trap word                                  |

| twi                    | TO,rA,SIMM       | Trap word immediate                        |

| xor[.]                 | rD,rA,rB         | XOR                                        |

| xorc[.]                | rD,rA,rB         | XOR with complement                        |

| xori                   | rD,rA,UIMM       | XOR with immediate                         |

| xoris                  | rD,rA,UIMM       | XOR with shifted immediate                 |

|                        |                  |                                            |